# Determining the junction temperature in a plastic semiconductor package, part 1

May 1st, 1999

By Bruce Guenin

Categories: Calculation Corner, Design, Materials, Compounds, Adhesives, Substrates, Plastics, Semiconductor, Test & Measurement

Issue: <u>May 1999</u>

Tags: Junction Temperature, Semiconductor Package

## No Comments. Be the first

**ShareThis**

## Print This

One of the primary tasks of the thermal engineer is to determine the temperature of the junction (active circuitry on an integrated circuit) for the various packages in a system. Measurements performed in the industry-standard test environment are often used in this endeavor. The most common thermal metric [1,2] is the junction-to-air thermal resistance,  $\Theta_{IA}$  (pronounced theta, ja) determined from the following equation

$$\Theta_{JA} = \frac{T_J - T_A}{P}$$

where  $T_J$  is the junction temperature,  $T_A$  is the temperature of the ambient air, and P is the total power dissipated by the device. This thermal metric is measured under standard, but artificial conditions. It is useful for comparing the thermal performance of various packages but often has limited relevance in determining  $T_J$  in the application.

For situations in which an actual system exists,  $T_J$  can be determined by a measurement of the temperature on the top center of the package,  $T_T$ , and the use of a more recently defined metric,  $\Psi_{TT}$ .

$\Psi_{JT}$  (pronounced psi, jt), or the junction-to-top thermal characterization parameter [1,2], is determined by taking a measurement in an industry-standard test environment and inputting the results into the following

Determining the junction temperature in a plastic semiconductor package...

equation:

$$\Psi_{JT} = \frac{T_J - T_T}{P}$$

The measurement should be performed with the same package used in the system, with approximately the same size die, and on a board with the same stackup (number of signal layers and power/ground planes). This equation has the same form as a thermal resistance calculation, but is not a true thermal resistance since the total power is used in the calculation and not the power flowing from the junction to the top of the package.

When used to calculate  $T_{I}$  in the application, this equation is rearranged as follows

$$T_J = T_T + P \Psi_{JT}$$

with  $T_T$  and P determined from the system environment.

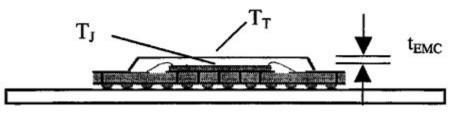

Although useful,  $\Psi_{JT}$ , is not yet commonly measured. However, it can be estimated for a package constructed with epoxy molding compound (EMC) above the die as shown in the figure, using a measured value of  $\Theta_{JA}$  in the following equation

$$\Psi_{JT} = \frac{h\Theta_{JA}t_{EMC}}{\kappa_{EMC}}$$

where h is the heat transfer coefficient.[3], and  $t_{EMC}$  and  $\kappa_{EMC}$  are the thickness and thermal conductivity of the EMC, respectively. The expression for  $\Psi$ JT is derived assuming that  $T_T - T_A - T_J - T_A$ . The physical basis for this equation is that the temperature difference between the junction and the package top is dependent upon the amount of heat flowing out of the top of the package, as determined by the magnitude of h.

The following table displays values of  $\Psi$ JT calculated for a PBGA (Plastic Ball Grid Array) package of the sort illustrated in the figure. In these calculations,  $t_{EMC}$  and  $\kappa_{EMC}$  are assumed to be 0.85 mm and 0.7 W/mK, respectively.

| V <sub>Air</sub> | h                   | <b>O</b> <sub>JA</sub> | <b>❷</b> <sub>JT</sub> |

|------------------|---------------------|------------------------|------------------------|

| m/s              | W/m <sup>2</sup> -K | °C/W                   | °C/W                   |

| 0                | 16                  | 16.7                   | 0.3                    |

| 1                | 30                  | 13.8                   | 0.5                    |

| 2.5              | 44                  | 12.5                   | 1.0                    |

Note that the calculated values of  $\Psi_{JT}$  increase as more heat is preferentially extracted out of the top of the package with increasing air velocity.

## References

1. JEDEC Standard, "Integrated Circuits Thermal Test Method Environment Conditions - Natural

Convection (Still Air)," EIA/JESD51-2.

2. JEDEC Standard, "Integrated Circuits Thermal Test Method Environmental Conditions – Forced Convection (Moving Air)," EIA/JESD51-6.

3. See Calculation Corner, Electronics Cooling Magazine, January, 1998, "Convection and Radiation," for a graph used to estimate h at various air velocities.

## **Related Articles**

# **Determining the junction temperature in a plastic semiconductor package, part II**

In the majority of applications involving plastic surface-mount packages, most of the heat generated by integrated circuits will flow to the printed circuit board (PCB) by way of the package leads and then to In...read more

# <u>Test methods for characterizing the thermal transmission properties</u> of phase-change thermal interface materials

All phase change thermal interface materials are designed to minimize the thermal resistance in an interface between a heat generating component and a heat sink. How well they achieve this goal in a specific application...<u>read more</u>

# <u> Thermal Vias – A Packaging Engineer's Best Friend</u>

Introduction In the 1990's, with the advent of surface mounting of semiconductor packages, multilayer printed circuit boards and multilayer substrates for Ball Grid Array packages were introduced. In order to create electrical interconnections between the...<u>read more</u>