Introduction

A circuit question walked into my cube the other day. An engineer in another group was working his way through an application note and he found the presentation unclear -- I agreed with him. The application note provided an approximate solution to a common problem in electrical engineering -- matching voltage and impedance levels between two different logic families. This engineer asked if I could provide a simpler solution to the problem that also provide an exact impedance match. I said I would take a look. This post documents my solution. To keep my presentation simple, I have not worried here about resistor and voltage tolerances. Rest assured that my ultimate solution will take the parametric uncertainties into account − I actually had a meeting this morning on this very topic.

This problem is related to a previous blog post where I solved this problem using a four-resistor matching network. The application note proposes a three-resistor matching network that provides a less optimal solution electrically but is easier to route on the Printed Circuit Board (PCB).

Background

Problem Description

Many of our hardware designs use FPGAs that have Low Voltage Differential Signal (LVDS) inputs. Unfortunately, the other hardware in our system uses Low-voltage Positive Emitter-Coupled logic (LVPECL). These two logic families have logic level differences that prevent them from being directly connected -- a matching network must be inserted between them. For the problem here, we will design a matching network that will shift the LVPECL levels to LVDS levels and will ensure that the input impedance of the FPGA receiver will match the characteristic impedance of the PCB.

Three-Resistor Matching Network

This blog post will compute resistor values for the three-resistor matching network (R1, R3, and R4) shown in Figure 1.

There are some specifics values we use for our circuit implementation:

- VTTRX = 1.2 V

This is the voltage that is connected to the termination resistor. The FPGA vendor specifies this voltage.

- VCCPECL = 3.3 V

The 3.3 V supply that powers our LVPECL circuits. It is a very commonly seen supply voltage.

Optimization Constraints

The three resistors must be chosen to meet four constraints:

- VIN (input LVDS voltage) must not exceed the FPGA's maximum input voltage (1.2 V).

The FPGA's LVDS receiver has a maximum input voltage that it can receive. Because the matching circuit is linear, the maximum input voltage occurs when the transmitter puts out its maximum level.

- Z0: input impedance = 50 Ω

Generally, this is one of the most important requirements. However, the application note treats this as of secondary importance. I will see if I can improve the conformance to this specification. Because the Printed Circuit Board (PCB) manufacturers have impedance tolerances of ~10%, exact matching is not that important.

- VTTRX (Termination Voltage) = 1.2 V

This is the Thevenin-equivalent voltage LVPECL driver sees as its load.

- ΔVIN (differential input voltage) must exceed the FPGA's required minimum level.

The difference between the input high and low levels must be greater than a minimum value to ensure that the receiver can distinguish between them.

There are different approaches you can take to choosing the three resistors. Generally, we try to set VTTRX and Z0 exactly because the LVPECL output driver is designed assuming specific values for the load circuit. My approach determined the values of R3 and R4 needed to set VTTRX and Z0 to specific values. The values of R3 and R4 were functions of R1. You then have two approaches to a solution:

- Vary R1 to set the maximum VIN value and verify that the minimum ΔVIN requirement is met.

- Vary R1 to maximize ΔVIN and verify that the maximum VIN value will not be exceeded.

I worked the problem both ways and got the same answer. In the main body of the blog, I will use approach #1. In Appendix B, I will use approach #2.

Analysis

The Mathcad worksheet containing this analysis is in this file (XML file, download it to your desktop and point Mathcad at it).

Equations and Constraints

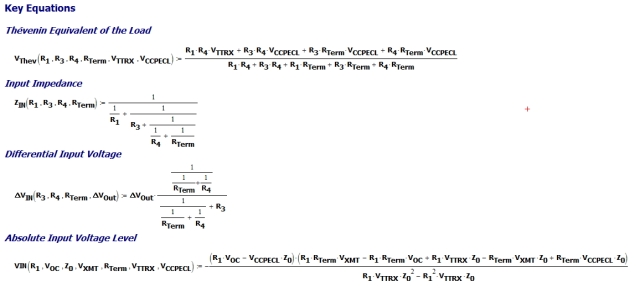

Figure 2 shows equations for the four constraints that must be satisfied.

Solution

Here is the approach that I used.

- Using nodal analysis, compute R1 assuming Z0= 50 Ω and VThev=1.3 V.

- Write an equation for the input LVDS voltage as a function of the LVPECL output voltage.

- Compute the value of R1 that ensure that the maximum LVDS input voltage occurs when for the maximum LVPECL output.

Figure 3 shows my solution in Mathcad. The transmit and receiver logic levels are documented in Appendix A.

Check Figures

Figure 4 shows my check of the solution that my component selection meets my needs.

Conclusion

My co-worker requested an exact solution to the matching part of the problem and I was able to calculate a set of resistor values that met his needs. As part of this effort, I also created a tool that allows him to experiment with non-matching values so that he can determine quickly if allowing some mismatch will give him any advantage.

Appendix A: Logic Levels

Transmit Levels

Figure 5 shows the LVPECL driver specifications. My calculations assume that VCC = 3.3 V. The key specifications in Figure 5 are:

- Minimum differential output voltage of 600 mV

- Maximum output voltage of

- Minimum output voltage of

Receive Levels

Figure 6 shows the LVDS receiver specifications. The key specifications in Figure 6 are:

- The absolute maximum input voltage is 1.2 V (listed as VMGAVTT, which is 1.2 V in our system)

- The minimum allowed differential voltage is 150 mV.

Appendix B: Solution Using Approach #2 − Maximizing the Differential Input Voltage

Figure 7 shows my derivation of the same resistor values assuming that we maximize the differential input voltage with the constraint of absolute maximum input voltage of 1.2 V. The Mathcad worksheet containing this analysis is in this file (XML file, download it to your desktop and point Mathcad at it).

Pingback: Yet Another FPGA Differential Termination Example | Math Encounters Blog