**MIL · STD · 275E**

31 December 1984

SUPERSEDING MIL - STD - 275D 26 APRIL 1978 MIL - STD - 1495 3 AUGUST 1973

# **MILITARY STANDARD**

# PRINTED WIRING FOR ELECTRONIC EQUIPMENT

DEPARTMENT OF DEFENSE Washington, DC 20301

Printed Wiring for Electronic Equipment

MIL-STD-275E

1. This Military Standard is approved for use by all Departments and Agencies of the Department of Defense.

2. Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to: Naval Electronic Systems Command, ATTN: ELEX-8111, Washington, DC 20363, by using the self-addressed Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document, or by letter.

# CONTENTS

|           |                                                                                      | AGE      |

|-----------|--------------------------------------------------------------------------------------|----------|

| Paragraph | 1. SCOPE                                                                             | 1        |

|           | 1.1 Purpose<br>1.2 Classification                                                    | 1        |

|           |                                                                                      | ĩ        |

|           | 2. REFERENCED DOCUMENTS                                                              | S        |

|           | 3. DEFINITIONS                                                                       | 4        |

|           | 4. GENERAL REQUIREMENTS                                                              | 5        |

|           | 4.1 Design features                                                                  | 5<br>5   |

|           | 4.2 Documentation<br>4.3 Master drawing                                              | 5        |

|           | 4.3 Master drawing<br>4.4 Printed-wiring assembly drawing                            | 7        |

|           | 4.5 Production master                                                                | 7        |

|           | 5. DETAIL BOARD REQUIREMENTS                                                         | 9        |

|           | 5.1 Conductive pattern                                                               | 8        |

|           | 5.2 Lands l                                                                          | .0       |

|           |                                                                                      | 3        |

|           |                                                                                      | 4        |

|           | sts stated to bugs notes                                                             | 4        |

|           |                                                                                      | 6        |

|           | 5.8 Detail board marking requirements 1                                              | 7        |

|           | 5.9 Quality conformance testing circuitry 1                                          | 7        |

|           |                                                                                      | 8        |

|           | 6.1 Approved methods of attachment 1                                                 | В        |

|           |                                                                                      | 9        |

|           |                                                                                      | 21<br>22 |

|           |                                                                                      | 22       |

|           | APPENDIX                                                                             |          |

|           |                                                                                      |          |

| Paragraph |                                                                                      | 23       |

|           | 10.1 Purpose 2                                                                       | 23       |

|           | 20. DESIGN CONSIDERATIONS 2                                                          | 3        |

|           | 20.1 Design process tolerances and allowance                                         | 3        |

|           | 20.2 Board dimensions                                                                | 23       |

|           |                                                                                      | 3        |

|           |                                                                                      | 23       |

|           |                                                                                      | 23       |

|           | 20.0 migh voitage lactors                                                            |          |

|           | TABLES                                                                               |          |

| Table     | 1. Conductor spacing                                                                 | 9        |

|           | II. Standard fabrication allowances for                                              | 1        |

|           | plated-through hole attachment l<br>III. Standard fabrication allowances for surface |          |

|           |                                                                                      | 2        |

|           | IV. Clad laminates 1                                                                 | 5        |

|           | V. Comformance test circuitry                                                        | 7        |

|           |                                                                                      | 4        |

# FIGURES

| Fί | 9 | u | r | e |  |

|----|---|---|---|---|--|

|----|---|---|---|---|--|

|     |                                                   | PAGE |

|-----|---------------------------------------------------|------|

| 1.  | Quality conformance test circuitry                | 26   |

| 2,  | Block diagram depicting typical printed wiring    |      |

|     | drawing relationships                             | 32   |

| 3.  | Use of grids in defining pattern requirements     | 33   |

| 4.  | Conductor thickness and width                     | 34   |

| 5.  | Discrete leadless component land pattern          | 38   |

| 6.  | Chip carrier land pattern                         | 38   |

| 7.  | Modified fan out patterns                         | 39   |

| 8.  | Heel mounting requirements                        | 39   |

| 9.  | Typical flat pack land                            | 40   |

| 10. | Coined or flattened lead lands                    | 40   |

| 11. | Annular ring requirements (External)              | 41   |

| 12. | Annular ring requirements (Internal)              | 41   |

| 13. |                                                   |      |

| 14. | Minimum annular ring dimensions (External)        | 41   |

| -   | Ground plane lands (typical)                      | 42   |

| 15. | Hole diameter for flat lead                       | 42   |

| 16. | Dielectric layer thickness measurement            | 43   |

| 17. | Location of test coupon based on number of boards |      |

|     | fabricated per panel                              | 44   |

| 18. | Flat lead termination                             | 45   |

| 19. | Lead bend                                         | 46   |

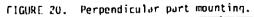

| 20. | Perpendicular part mounting                       | 46   |

.

#### 1. SCOPE

1.1 Purpose. This standard establishes design requirements governing rigid, single-sided printed-wiring boards, double-sided printed-wiring boards, multilayered printed-wiring boards, printed-wiring assemblies constructed from those boards mentioned above, and design considerations for the mounting of parts and assemblies thereon. The design criteria (such as electrical spacings) contained in this standard are predicated on the requirement that end item assemblies (circuit card assemblies, printed-wiring assemblies, back planes, mother boards) shall be conformally coated (see 6.3.1). Conformal coating shall be in accordance with MIL-I-45058.

1.2 <u>Classification</u>. Printed-wiring boards shall be of the types shown, as specified (see 4.2):

Type 1 - Single-sided board Type 2 - Double-sided board Type 3 - Multilayer board

.

.

# 2. REFERENCED DOCUMENTS

#### 2.1 Government documents.

.

2.1.1 Specifications, standards, and handbooks. Unless otherwise specified, the following specifications, standards, and handbooks, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards (DoDISS) specified in the solicitation, form a part of this standard to the extent specified herein.

.

#### SPECIFICATIONS

FEDERAL

.

| L-F-340     | - | Film, Sensitized, Wash-Off Process, Diazotype, Moist and                                                                                                                      |

|-------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QQ-B-626    | - | Dry Process, Brownprint, Roll and Sheet.<br>Brass, Leaded and Nonleaded Rod, Shapes, Forgings and Flat                                                                        |

| QQ-B-750    | - |                                                                                                                                                                               |

| QQ-C-576    | - | and Structural and Special Shaped Sections.<br>Copper Flat Products with Slit, Slit and Edge-Rolled,<br>Sheared, Sawed, or Machined Edges, (Plate, Bar, Sheet, and<br>Strip). |

| QQ-N-290    | - | Nickel Plating (Electrodeposited).                                                                                                                                            |

| QQ-5-571    | - | Solder; Tin Alloy; Lead-Tin Alloy; and Lead Alloy.                                                                                                                            |

| MILITARY    |   |                                                                                                                                                                               |

| MIL-D-8510  | - | Drawings, Undimensioned, Reproducibles, Photographic and Contact, Preparation of.                                                                                             |

| MIL-P-13949 | - | Plastic Sheet, Laminated, Metal-Clad (For Printed Wiring),<br>General Specification for.                                                                                      |

| MIL-C-14550 | - |                                                                                                                                                                               |

| M1L-P-28809 | - | Printed-Wiring Assemblies.                                                                                                                                                    |

| MIL-G-45204 | _ | Gold plating, Electrodeposited.                                                                                                                                               |

| MIL-I-46058 | - | Insulating Compound, Electrical (For Coating Printed Circuit Assemblies).                                                                                                     |

| MIL-P-55110 | - | Printed-Wiring Boards.                                                                                                                                                        |

| MIL-P-81728 | - | Plating, Tin-Lead, Electrodeposited.                                                                                                                                          |

STANDARDS

MILITARY

| DDD-STD-100  |   | Engineering Drawing Practices.                             |

|--------------|---|------------------------------------------------------------|

| MIL-STD-130  | - | Identification Marking of U.S. Military Property.          |

| DOD-STD-1686 | _ | Electrostatic Discharge Control Program For Protection of  |

|              |   | Electrical and Electronic Parts, Assemblies and Equipment. |

(Copies of specifications, standards, drawings, and publications required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting officer.)

2.2 Other publications. The following documents form a part of this standard to the extent indicated herein. The issues of the documents which are indicated as DOD adopted shall be the issue listed in the current DoDISS and the supplement thereto, if applicable.

AMERICAN NATIONAL STANDARDS INSTITUTE (ANSI)

| ANSI-Y14.5 | - | Dimensioning and Tolerancing for Engineering Drawings. |

|------------|---|--------------------------------------------------------|

| ANSI-Y14.1 | - | Drawing Sheet Size and Format                          |

#### MIL-STD-275E

#### 31 December 1984

(Application for copies should be addressed to the American National Standards Institute, Inc., 1430 Broadway, New York, NY 10018.)

AMERICAN SOCIETY FOR TESTING AND MATERIALS (ASTM)

ASTM - E53 - Standard Method for Chemical Analysis of Copper (Electrolytic Determination of Copper).

(Application for copies should be addressed to the American Society for Testing and Materials, 1916 Race Street, Philadelohia, PA 19103.)

INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

IEEE-STD-200(ANSI Y3?.16) - Reference Designations for Electrical and Electronic Parts and Equipments.

(Application for copies should be addressed to Institute of Electrical and Electronics Engineers Service Center, ATTN: Publication Sales, 445 Hose Lane, Piscataway, NJ 08854.)

INSTITUTE FOR INTERCONNECTING AND PACKAGING ELECTRONIC CIRCUITS (IPC)

| 1 P C - T - 50 | - Terms and Definitions.                                                                                             |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| 1PC-CF-150     | <ul> <li>Copper Foil for Printed Wiring Applications.</li> </ul>                                                     |

| 1PC-D-350      | - End Product Description in Numeric Form.                                                                           |

| IPC-S-815      | <ul> <li>General Requirements for Soldering Electronic<br/>Interconnections.</li> </ul>                              |

| 1PC-5M-840     | <ul> <li>Qualification and Performance of Permanent Polymer<br/>Coating (Solder Mask) for Printed Boards.</li> </ul> |

(Application for copies should be addressed to the Institute for Interconnecting and Packaging Electronic Circuits, 3451 Church Rd., Evanston, IL 60203.)

2.3 Order of precedence. In the event of a conflict between the text of this standard and the references cited herein, the text of this standard shall take precedence.

.

. . . . . . . . .

#### 4. GENERAL REQUIREMENTS

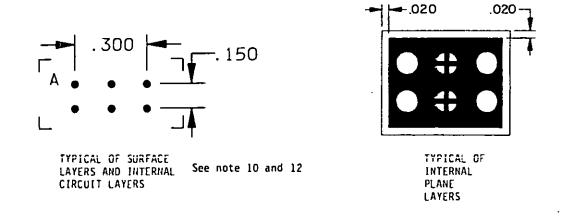

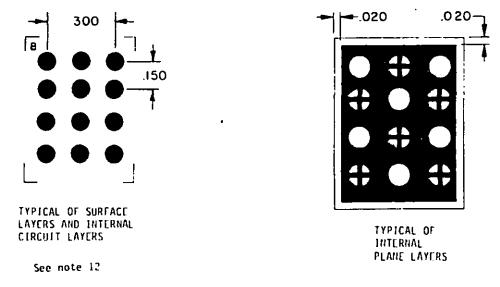

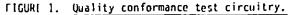

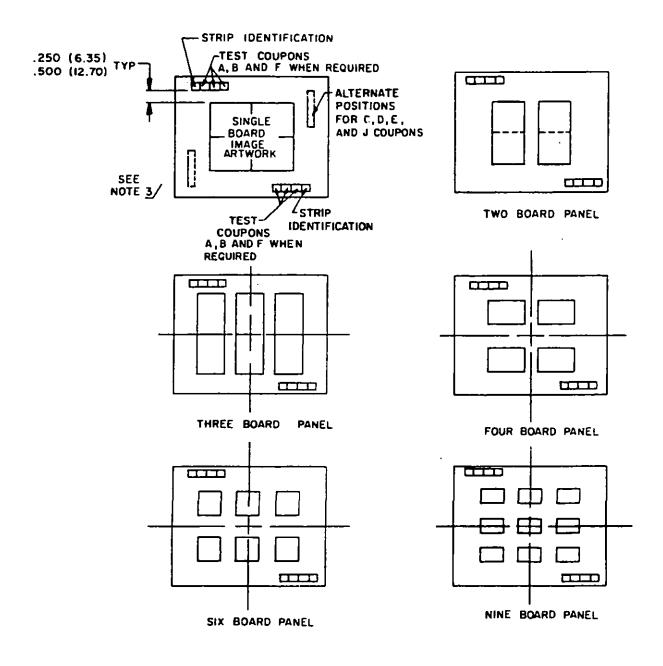

4.1 Design features. The design features of the printed-wiring boards shall be in accordance with this standard. Quality conformance test circuitry shall also be included on the production master. Quality conformance test circuitry shall be included on each panel and shall be in accordance with figure 1 and 5.9. Test circuitry shall be not more than 0.5 inch (13 mm) and shall be not less than 0.25 inch (6.4 mm) from the edge of the printed board, and represents all the manufacturing processes such as drilling, plating, etching, fusing, ground/voltage/ thermal/mechanical planes or cores, separately fabricated layers, permanent coatings (solder mask) and so forth.

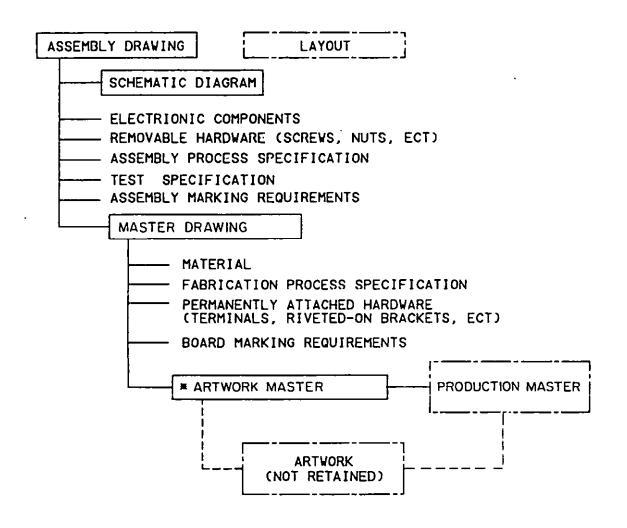

4.2 <u>Documentation</u>. Requirements for drawing content may be satisfied by direct delineation on the drawing or by reference to other documents which are part of the engineering drawing set (see figure 2.).

4.2.1 <u>Reference designations</u>. Reference designations of components to be mounted on printed-wiring boards, when specified on the master drawing or the printed-wiring assembly drawing, shall be in accordance with IEEE-STD-200.

4.2.2 <u>Deviation request and approval</u>. When a deviation to this standard is necessary, or has been granted in the initial contract design description, the contractor (before proceeding further) shall furnish each proposed master drawing, or a detailed deviation request to the Government Agency concerned for approval with justification for the deviation. If approved, all deviations granted shall be documented on the master drawing.

4.2.3 <u>Government furnished master drawings</u>. Any deviation from this standard or drawing shall have been recorded on the Government approved master drawing or a Government approved deviations list. When new or additional deviations from this standard or drawing are necessary, the contractor (before processing further) shall furnish one copy of each proposed master drawing being revised, or a detailed deviation request to the Government Agency concerned for approval with justification for the deviation. If approved, all deviations granted shall be documented on the master drawing or the Government approved deviations list.

4.2.4 <u>Conflicts</u>. In the event of any conflict between the approved master drawing supplemented by an approved deviation list, if applicable, and the requirement of this standard, the approved master drawing and deviations list shall take precedence.

4.3 <u>Master drawing</u>. The master drawing shall be prepared in accordance with DOD-STD-100; shall include all appropriate detail board requirements (see section 5), and the following:

- a. The type, size, and shape of the printed-wiring board.

- b. The size, location, and tolerance of all holes therein.

- c. Etchback allowances, when required or permitted.

- d. Location of traceability marking.

- e. Dielectric separation between layers.

- f. Shape and arrangement of both conductors and nonconductor patterns defined on each layer of the printed-wiring board. Copies of the production masters or copies of the artwork may be used to define these patterns.

- g. Separate views of each conductor layer.

- h. Any and all pattern features not controlled by the hole sizes and locations shall be dimensioned either specifically, or by reference to the grid system (see n).

- i. Processing allowances that were used in the design of the printed-wiring board (see 5.1.1, 5.1.4, 5.2.1.2, 5.2.2, and 5.2.2.6).

- j. All notes either included on the first sheet(s) of the master drawing or by specifying the location of the notes on the first sheet.

- k. Conductor layers numbered consecutively starting with the component side as layer 1. If there are no conductors or lands on the component side, the next layer shall be layer 1. For assemblies with components on both sides, the most densely populated side shall be layer 1.

- 1. Identification marking (see 5.8).

- m. Size, shape, and location of reference designation and legend markings, if required (see h).

- n. A modular grid system to identify all holes, test points, lands, and overall board dimensions with modular units of length of 0.100, 0.050, 0.025, or other multiples of 0.005 inch in that order of preference. For design where the majority component locations are metric-based (SI), the basic modular units of length shall be 2.0, 1.0, 0.5, or other multiples of 0.1 mm in that order of preference. The grid system shall be applied in the X and Y axes of the Cartesian coordinates. The grid shall not be reproduced on the master drawing; but may be indicated using grid scales or X, Y control dimensions (see figure 3).

- Dimensions for critical pattern features which may effect circuit performance because of distributed inductance or capacitance effects within the tolerance required for circuit performance.

- p. All terms used on the master drawing shall be in conformance with the definitions of ANSI/IPC-T-50 or ANSI Y14.5 (see 3.1 and 2.2).

- q. Deviations to this standard (see 4.2.2).

- r. Minimum line width and spacing of the finished printed-wiring board.

- s. Maximum rated voltage (maximum voltage between the two nonconnected adjacent conductors with the greatest potential difference) for type 3 boards only.

- t. Plating and coating material(s) and thickness(es).

- u. Identification of test points required by the design (see 5.1.8).

- Applicable fabrication specification with date(s), revision letter, and amendment number.

When continuation sheets of a drawing are used for conductor pattern definition, they need not be prepared on standard drawing forms provided standard sheet sizes are used with standard continuation sheet title blocks in accordance with ANSI Y14.1 located in the lower right corner of each sheet. Numeric form of end product descriptions shall be in accordance with IPC-D-350.

4.3.1 <u>Hole location tolerance</u>. Unless otherwise specified, the location of holes shall be dimensioned with respect to single or secondary grid systems. Each distinctive hole pattern (such as, plated-through holes, tooling holes, mounting holes, windows, access holes, and so forth), may require separate consideration or specification of tolerance. Producibility considerations are presented in table VI.

4.3.2 <u>Processing allowances</u>. The processing allowances which were considered in the design and artwork preparation for the printed-wiring board shall be documented and defined on the master drawing in either note form or by reference to another drawing which contains artwork requirements or specifications. This information shall be expressed in terms of the maximum variation between the end-product conductor widths and spacings and what may appear on the artwork; the minimum land, in reference to the drilled or plated hole and what may appear on the artwork; or any other feature conditions considered in the design where the variation between end-product and artwork configuration play a role in the producibility of the printed-wiring board.

4.3.3 <u>Datums</u>. There shall be a minimum of two datum features to establish the mutually perpendicular datum reference frame for each board. These datums shall be established by at least two holes, points, symbols, or other datum features, but not edges. Critical design features may require the use of more than one set of datum references. The master drawing shall establish the relationship and acceptable tolerance between all datums features. All datum features shall be located on grid or establish grid criterion, as defined on the master drawing, and should be on or within the outline of the printed-wiring boards.

# MIL - STD - 275E

#### 31 December 1984

4.4 Printed-wiring assembly drawing. The printed-wiring assembly drawing shall cover printed-wiring on which separately manufactured parts have been added. The printed-wiring assembly drawing shall be in accordance with DOD-STD-100 and should include at least the following:

- Parts and material list. а.

- b. Component mounting and installation requirements.

- Cleanliness requirements per MIL-P-28809. с.

- Location and identification of materials or components (or both). đ.

- Component orientation and polarity. e.

- f.

- Applicable ordering data from MIL-P-28809. Structural details when required for support and rigidity. q.

- Electrical test requirements. h.

- Marking requirements. i.

- Electrostatic discharge protection requirements. j.

- Special solder plug requirements. k .

- Eyelets and terminals. ۱.

- Lead forming requirements. ω.

- Type of conformal coating and masking. n.

- ο. Solder mask.

- Traceability. D.

The printed-wiring assembly drawing shall include the definition of any conditions considered in the design where the manufacturing variation between the end product and assembly configuration play a role in the producibility or performance of the printed-wiring assemblies.

4.4.1 <u>Deviation request and approval</u>. When a deviation to this standard is necessary, or has been granted in the initial contract design description, the contractor (before proceeding further) shall furnish each proposed assembly drawing, or a detailed deviation request to the Government Agency concerned for approval with justification for the deviation. If approved, all deviations granted shall be documented on the assembly drawing.

4.4.2 Government furnished assembly drawings. Any deviation from this standard or the drawing shall have been recorded on the Government approved assembly drawing or a Government approved deviations list. When new or additional deviations from this standard or the drawing are necessary, the contractor (before proceeding further) shall furnish one copy of each proposed assembly drawing being revised, or a detailed deviation request to the Government Agency concerned for approval with justification for the deviation. If approved, all deviations granted shall be documented on the assembly drawing or the Government approved deviations list.

4.4.3 <u>Conflicts</u>. In the event of any conflict between the approved assembly drawing supplemented by an approved deviation list, if applicable, and the requirement of this standard, the approved assembly drawing and deviations list shall take precedence.

4.5 Production master. When specified in the contract or purchase order, a production master of each layer shall be provided as part of the drawing set. When a production master is not supplied, the manufacturer shall be responsible for the preparation of the production master with sufficient accuracy to meet the requirements of the printed wiring detailed on the master drawing. The production master shall be as defined in IPC-T-50 and shall be supplied or prepared on 0.0075 \*0.0005 inch thick biaxially oriented, dimensionally stable polyester type film or equal, in accordance with MIL-D-8510, type II: L-F-340 film, photographic subclass a, class 2, type I or II, style IA or photographic glass plates. The accuracy of the production master (single image, multiple image, or any associated quality assurance coupons) shall be such that the lands, conductors, and other features shall be located within 0.004 inch diameter of the true grid position established for the layer, and that for the composite production master, the features of all layers shall coincide within 0.006 inch diameter of the true grid position, when measured at 20°C \*1°C, and 50 \*5 percent relative humidity after the material has stabilized. In the event that tighter tolerances are required in order to produce printed wiring, the production master precision requirements as considered in the design process, shall be defined on the master drawing.

# MIL-ST0-275E

31 December 1984

# 5. DETAIL BOARD REQUIREMENTS

#### 5.1 Conductor pattern.

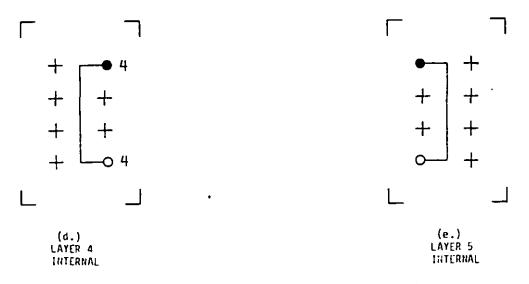

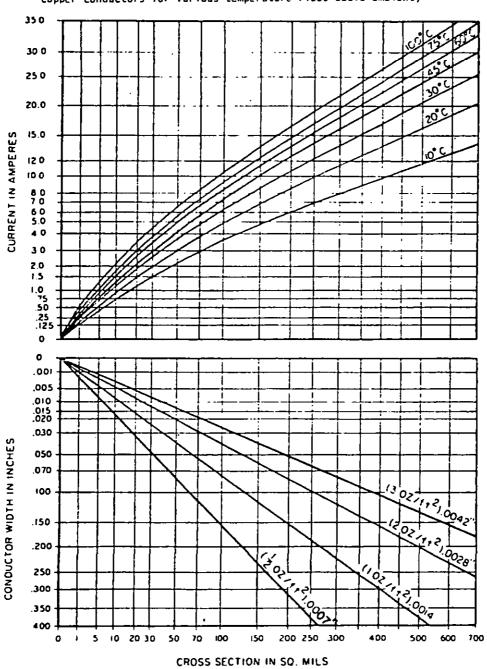

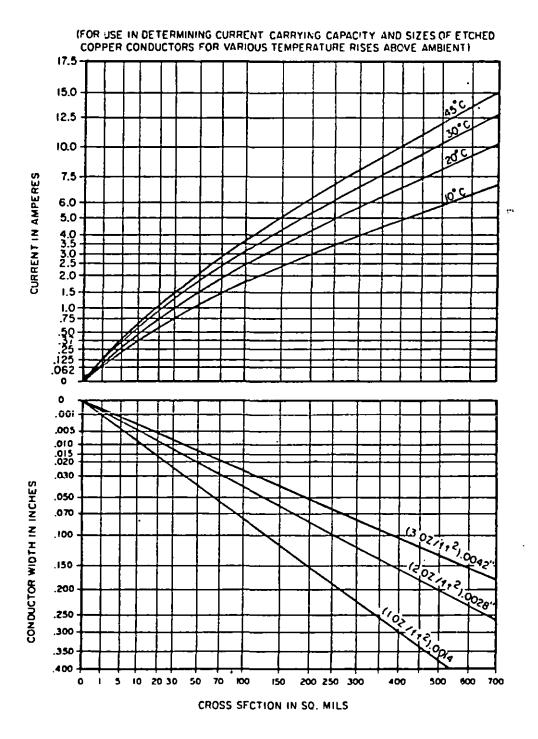

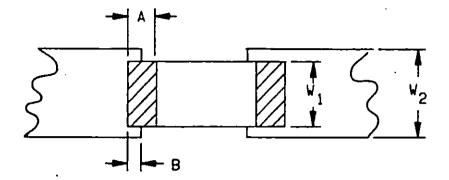

5.1.1 <u>Conductor thickness and width</u>. The width and thickness of conductors on the finished printed-wiring board shall be determined on the basis of the current carrying capacity required. The temperature rise shall be determined in accordance with figure 4a for type 1, type 2, and external layers of type 3 boards, and figure 4b for internal layers of type 3 boards. For ease of manufacture and durability in usage conductor width and spacing requirements shall be maximized while maintaining the minimum spacing requirements of table I. The minimum conductor width shown on the master drawing shall be not less than 0.004 inch (0.10 mm). To maintain the conductor width shown on the master drawing, the line widths on the production master shall be compensated for process allowances as shown in 20.1 and table VI of the appendix.

5.1.2. <u>Conductors with less than 90<sup>°</sup> included angle</u>. All conductors that change direction where the included angle is less than 90<sup>°</sup> shall have the external corners of the conductor rounded.

5.1.3 <u>Conductors</u>. The length of a conductor between any two lands should be held to a minimum. However, conductors which are straight lines and run in X, Y, or 45<sup>°</sup> directions in general are preferred to aid computerized documentation for mechanized or automated layouts.

5.1.4 <u>Conductor spacing</u>. Larger spacings shall be used whenever possible and the minimum spacing between conductors, between conductor patterns, and between conductive materials (such as conductive markings or mounting hardware) and conductors shall be in accordance with table I, and defined on the master drawing. To maintain the conductor spacing shown on the master drawing, space widths on the production master shall be compensated for process allowances as shown in 20.1 and table VI of the appendix. Plated-through holes passing through internal foil planes (ground and voltage) and thermal planes shall meet the same minimum clearance between the plated-through hole and foil or ground planes as required for spacing between internal conductors.

| TABLE I. Conduc | tor s | pacing. |

|-----------------|-------|---------|

|-----------------|-------|---------|

| Voltage between conductors                                 | Minimum                                                                                                           | spacing                                                                                                              |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| 1 DC or AC peak (volts)                                    | T Surface layers                                                                                                  | Internal layers 1                                                                                                    |  |

| 0-100<br>101-300<br>301-500<br>Greater than 500 <u>1</u> / | 10.005 inch (0.13 mm)<br>10.015 inch (0.38 mm)<br>10.030 inch (0.76 mm)<br>10.00012 inch (.00305 mm)<br>1per volt | 0.004 inch (0.10 mm)<br> 0.008 inch (0.20 mm)  <br> 0.010 inch (0.253 mm)  <br> 0.0001 inch (.0025 mm) <br> per volt |  |

1/ For reference only, voltages greater than 500 should be evaluated for the specific design application.

5.1.5 Edge spacing. The minimum spacing between conductive patterns and the edge of the printed-wiring board or any adjacent conductive surface, such as supporting structure or frames (nonmoving), shall be not less than the minimum spacing specified in table I plus .D15-inch (0.38 mm), provided the edges are protected from physical harm in the installed assembly configuration. Printed wiring not so protected shall have a minimum conductor to edge distance of 0.050 inch (1.25 mm). The edge spacing requirement is not applicable to heat sinks and ground planes. To maintain the edge spacing shown on the master drawing, the edge spacings shall be compensated for process allowances as shown in 20.1 and table VI of the appendix.

5.1.6 Large conductive areas. Large conductive areas increase the likelihood for blistering or bowing during the soldering operation. The pattern and location of large conductive areas should be per 5.1.6.1 and 5.1.6.2. Design of conductive areas should provide balanced construction and include the use of nonfunctional copper, if practical.

5.1.6.1 Large external conductive areas. External conductive areas that extend beyond a 1-inch diameter circle should contain etched areas that will break up the large conductive area but will retain the continuity and functionality of the conductor. If etched areas are not provided, other methods should be used to minimize blistering or bowing. Large conductive areas should, if possible, be on the component side of the board. If solder mask is employed, over melting metals, conductive areas larger than 0.050 inches wide shall not be employed under the solder mask, see IPC-SM-840 and 20.5 of the appendix.

5.1.6.2 Large internal conductive areas (type 3). When a conductive area that extends beyond a 1-inch diameter circle is used on an internal layer, the layer should be placed as near the center of the board as possible and should contain etched areas that will break up the large conductive area but will retain the continuity and functionality of the conductor. If more than one internal layer has a large conductive area, the layers should be located in the board to provide balanced construction. For surface preparation considerations see 20.5 of the appendix.

5.1.7 <u>Interfacial connections</u>. Interfacial connections on type 2 and 3 printed-wiring boards shall be made by use of plated-through holes only. Wires, standoff terminals, eyelets, rivets, or pins shall not be used to provide interfacial connections.

5.1.7.1 Solder fillets and plugs. Printed-wiring boards subjected to wave or dip soldering shall be designed to facilitate flow of solder around component leads in plated-through holes and into plated-through holes without leads, so as to create a solder plug. Careful consideration shall be given to hole-to-lead diameter clearance (see 5.3.2 and 5.5) hole to board thickness ratios and heat relief of metal planes to promote solder plugging. In the event solder plugging due to natural capillary action is not possible, such as when a heat sink is bonded directly over plated-through holes, the design shall include provision for prevention of solder, flux or other chemicals from entering the plated-through hole. Solder may be prevented from entering the holes by prefilling these holes with an appropriate polymer plug, covering the holes with a sheet of permanent bonded material, tenting the holes with a permanent solder mask or blocking these holes with some temporary technique that will prevent solder access to the hole. All techniques must have sufficient durability to not break up when exposed to the solder process. The printed-wiring assembly drawing shall define the absence of such solder plug requirements. As a minimum solder plugs shall be required in:

- a. All electrically functional and nonfunctional plated-through holes with a lead; the lead is required to be surrounded 360° by the solder plug no matter what technique for soldering is used.

- b. Any plated-through hole without a lead, that is subject to wave or dip soldering with the degree and percentage of hole plugging described by the appropriate assembly or soldering specification (MIL-P-288D9, IPC-S-B15).

# MIL-STD-275E

#### 31 December 1984

Solder plugs are not necessarily required in:

- a. Any unsupported hole without a lead.

- b. Nonfunctional plated-through holes (hand soldered or vapor phase reflowed assembly).

- c. Any electrically functional plated-through hole (without a lead) not subjected to wave or dip soldering.

- d. Any plated-through hole covered with permanent solder mask, other polymeric cover layer (not conformal coating) or is already filled with an appropriate polymer in order to prevent hole access during wave or dip soldering.

- e. Any plated-through hole, electrically functional or not, without a lead, where access to the hole is limited by components, heat sinks, by design (blind vias), or where access of solder to the hole is prevented during the solder process.

5.1.9 Test points. When required by the design, test points for probing shall be provided as part of the conductor pattern and shall be identified on the master drawing and the assembly drawing. These "probe points" shall require that a land be available for probing as opposed to a conductor. Vias or component lead mounting lands may be considered as probe points provided that sufficient area is available for probing and maintaining the integrity of the via or component lead mounting joint. Probe points shall meet the plating requirements of 5.5.4.

5.2 Lands. Lands shall be provided for each point of attachment of a part lead or other electrical connection to the printed-wiring board.

5.2.1 Lands for through hole attachment. When through hole attachment is required, all of the requirements of 5.2 shall be considered in the design of the printed-wiring board except where 5.2.2 applies for surface attachment.

5.2.1.1 Lands location. The lands shall completely surround and abut on the mounting holes except where 5.2.2 and 5.2.6 applies.

5.2.1.2 Through hole land area requirements. The minimum diameter of the land surrounding an unsupported hole shall be at least 0.040 inch (1.02 mm) greater than the maximum diameter of the hole. When eyelets or standoff terminals are used, the lands on type 1, type 2, and external layers of type 3 boards shall be so designed as to have a minimum diameter of at least 0.020 inch greater than the maximum diameter of the projection of the eyelet or standoff terminal flange. The minimum diameter of a land surrounding a plated-through hole on type 2 and type 3 boards shall be determined by considering the following:

- a. Maximum diameter of the drilled hole.

- b. Minimum annular ring requirements (see 5.2.3). Etchback, when required, will reduce the insulation area that supports the internal land. The minimum annular ring considered in the design shall be not less than the maximum etchback allowed.

- c. A standard fabrication allowance, determined by statistical survey, which considers production master tooling and process variations required to fabricate boards (see table II).

# MIL-STD-275E

#### 31 December 1984

| <br> Greatest board/panel dimension  <br>                      | Preferred<br>inches | Standard  <br>inches | Reduced<br>producibility<br>inches |

|----------------------------------------------------------------|---------------------|----------------------|------------------------------------|

| Up to 12 inches                                                | 0.028               | 0.020  <br>          | 0.012 <u>1</u> /                   |

| I More than 12 inches I<br>I I I I I I I I I I I I I I I I I I | 0.034               | 1 0.024 1            | 0.016 <u>1</u> /                   |

TABLE II. Minimum standard fabrication allowances for plated-through hole attachment.

The above considerations shall be incorporated into the minimum land area provided on the production master such that: Minimum land diameter = a+2b+c. All lands and annular rings shall be maximized wherever feasible, consistent with good design practice and electrical clearance requirements.

1/ For copper weights greater than 1 oz/sq.ft., add 0.002 inch minimum to the fabrication allowance for each additional oz/sq.ft. of copper used.

5.2.2 Lands for surface attachment. When surface attachment is required, al) of the requirements of 5.2 shall be considered in the design of the printed-wiring board except where 5.2.1 and 5.2.6 apply. The selection, design, and position of the land geometry in relation to the part may significantly impact the solder joint. The designer must understand the capabilities and limitations of the manufacturing and assembly operations.

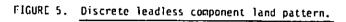

5.2.2.1 Lands for end-capped discrete components. Discrete components, when mounted as defined in 6.2.12.3, shall have their land relationships identified as shown on figure 5.

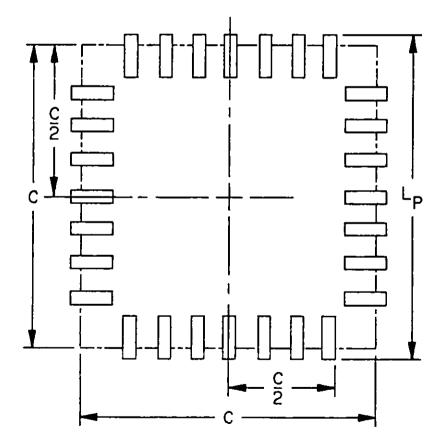

5.2.2.2 Land pattern for leadless chip carriers. The attachment lands for surface mounting leadless chip carriers should be the same width as the component terminal (castilation maximum) plus 0.005 inch (0.01 mm) whenever possible. The land length should extend between 0.015 inch to 0.04 inch (0.38 to 1.02 mm) beyond the maximum chip carrier outline on all four sides to create a horizontal solder fillet length equal to the vertical fillet rise (see figure 6). The design of fan-out to interconnect the hasic land pattern to other circuitry/devices is dependent on wiring density, testability, assembly, repairability, and routability requirements. Figure 7 shows some examples of possible fan-out patterns for leadless chip carriers. Chip carrier land sites should be located on a fixed grid within the printed board to optimize testing. This grid should be compatible with assembly and testing equipment so as to minimize the amount of specialized and complex equipment necessary.

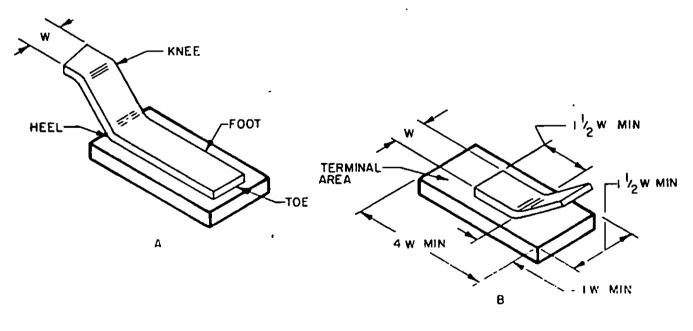

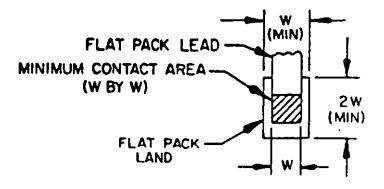

5.2.2.3 Lands for leaded chip carriers. The land size for ceramic and for leaded chip carriers should match the lead configurations. J shaped leads should have the land width he equal to or 0.005 inch larger than the width of the lead. The land length should extend between 0.015 inch to 0.040 inch (0.38 to 1.02 mm) beyond both sides of the foot of the J pattern. Other types of leads used for chip carriers should have the land commensurate with the lead configuration, in order to create a horizontal solder fillet length at the toe and heel of the lead configuration, as shown on figure 8.

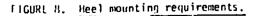

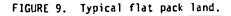

5.2.2.4 Lands for ribbon leaded surface mounted parts. The land requirements for mounting ribbon leaded parts, such as "flat packs", "quad packs", or small outline devices, shall preferably be rectangular. The minimum land width shall be equal to or exceed the maximum lead width by the amount shown on figure 8 providing room for both solder fillets at both the heel and toe of the ribbon lead. The minimum land width shall be approximately one and one-half times the width of the lead, or 0.005 inch (0.13 mm), whichever is less (see figure 9). Flat pack termination shall he staggered to permit greater spacing wherever possible. The center position of ribbon leaded components should be on a fixed grid, wherever possible, to facilitate testing.

5.2.2.5 Lands for flattened round leads. Flattened round leads shall have a land which will provide the seating so that the heel and the terminal relationship is in accordance with figure 10. Leads shall be seated with no side overhang. Toe overhang is acceptable, provided that the flattened lead in contact with the terminal area is a minimum of 150 percent of the unflattened lead diameter and the overhang does not reduce the spacing to adjacent parts to less than that specified on the assembly drawing.

5.2.2.6 Lands for plated-through holes (vias for boards with surface attached parts). The minimum diameter of a land surrounding a plated-through hole on type 2 and type 3 boards where surface attachment is used shall be determined by considering the following:

- a. Maximum diameter of the drilled hole.

- b. Minimum annular ring (see 5.2.3). Etchback, when required, will reduce the insulation that supports the internal land. The minimum annular ring

- considered in the design shall be not less than the maximum etchback allowed. c. A standard fabrication allowance, determined by statistical survey, which considers tooling production master and process variations required to fabricate boards (see table III).

| TABLE III. | Minimum | standard | fabrication allowances | . for surface | attachment. |

|------------|---------|----------|------------------------|---------------|-------------|

|            |         |          |                        |               |             |

| Greatest board/panel dimension | Preferred<br>inches | Standard  <br>inches | Reduced<br>producibility<br>inches |

|--------------------------------|---------------------|----------------------|------------------------------------|

| Up to 12 inches                | +0.026              | +0.018               | +0.010 <u>1</u> /                  |

| More than 12 inches            | +0.032              | +0.022               | +0.014 <u>1</u> /                  |

The above considerations shall be incorporated into the minimum land provided on the master pattern such that: Minimum land diameter = a+2b+c. All lands and annular rings shall be maximized wherever feasible, consistent with good design practice and electrical clearance requirements.

1/ For copper weights greater than 1 oz/sq.ft., add 0.002 inch minimum to the fabrication allowance for each additional oz/sq.ft. of copper used.

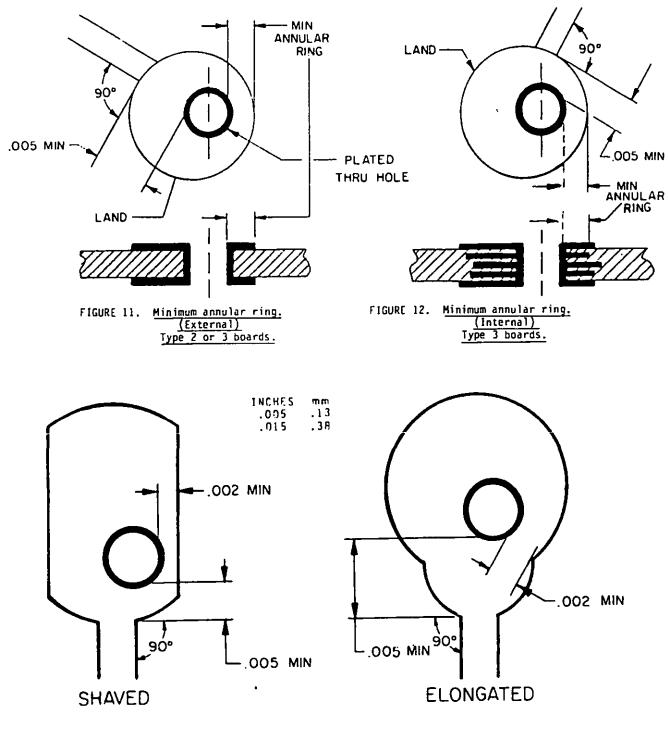

5.2.3 <u>Annular ring considerations</u>. The minimum annular ring on external layers is the minimum amount of copper (at the narrowest point) between the edge of the hole and the edge of the land after plating of the hole. The minimum annular ring on internal layers is the minimum amount of copper (at the narrowest point) between the edge of the drilled hole and the edge of the land after drilling the hole.

- External The minimum annular ring for an unsupported hole shall be 0.015 inch. The minimum annular ring for a plated-through hole in type 2, and external layers of type 3 boards shall be 0.002 inch, except where the conductor joins the land the annular ring shall be 0.005 inch minimum (see figures 11 and 13).

- Internal The minimum annular ring for internal lands on type 3 boards shall be 0.002 inch (see figure 12). Etchback, when required, will reduce the insulation supporting the annular ring of internal lands. The minimum annular ring considered in the design shall be not less than the maximum etchback allowed.

5.2.4 Nonfunctional lands (type 3, internal layers). Nonfunctional lands may be included on internal layers of type 3 boards. They need not be used where electrical clearance requirements do not permit, such as, ground planes, voltage planes and thermal planes. Plated-through holes passing through internal foil planes (ground and voltage) and thermal planes shall meet the same minimum spacing requirements as that for conductors on internal layers (see table I).

5.2.5 Thermal relief in conductor planes. Thermal relief is only required for holes that are subject to soldering. Connections associated with large conductor areas (ground planes, voltage planes, thermal planes, etc.) shall have a land that is relieved locally in the area of the plated-through hole connection in a manner similar to that shown on figure 14. When electrical considerations preclude the use of this technique, approval to deviate shall be obtained from the acquiring activity.

5.2.6 <u>Offset lands</u>. Lands, when used in conjunction with clinched leads, may be located adjacent to (not surrounding) the lead termination hole. The land shall be a sufficient distance from the hole to allow clipping of the part lead prior to unsoldering the part lead from the land.

5.3 Holes.

5.3.1 <u>Quantity</u>. A separate component hole shall be provided for each lead or terminal of a part or end of wire jumper except as specified in 5.2 and 6.2.14.

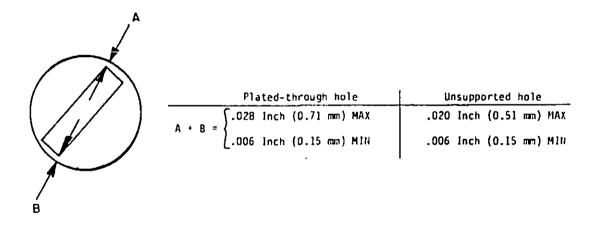

5.3.2 Diameter of unsupported holes. The diameter of an unsupported terminal hole shall not exceed by more than 0.020 inch (0.51 mm) and shall be not less than 0.006 inch (0.15 mm) the nominal diameter of the lead to be inserted, unless it is clinched. The number of different hole sizes shall be kept to a minimum. When flat ribbon leads are mounted through unsupported holes, the difference between the nominal diagonal of the lead and the inside diameter of the unsupported hole shall not exceed 0.020 inch (0.51 mm) and shall be not less than 0.006 inch (0.15 mm), as shown on figure 15.

5.3.3. Eyelet hole diameter. Eyelets shall not be used in new design unless approved by the Government acquiring activity. When eyelets are used, the diameter of holes in which eyelets are inserted shall not exceed the outside diameter of the barrel of the eyelet by more than 0.006 inch (0.25 mm). The maximum inside diameter of the eyelets shall be not more than 0.028 inch (0.71 mm) greater or less than 0.006 inch than the nominal diameter of the lead or terminal to be inserted in the eyelet, unless the lead is clinched (see 6.1.2). Interconnections shall not be made with eyelets.

5.3.4. <u>Spacing of adjacent holes</u>. The spacing of unsupported or plated-through holes (or both) shall be such that the lands surrounding the holes meet the spacing requirements of 5.1.4. The spacing between adjacent holes of any other type shall be not less than the printed-wiring board thickness or the hole diameter, whichever is smaller.

5.3.5 Location. All land and hole locations shall be at the grid intersections of the modular dimensioning system (see 4.3) controlled by either primary or secondary grid systems (see 4.3.1) used for printed wiring except as specified in 5.3.5.1.

5.3.5.1 <u>Pattern variations</u>. Parts whose leads emanate in a pattern which varies from the grid intersections established by the master drawing shall be mounted or attached to the printed-wiring board with one of the following hole patterns:

- a. A hole pattern where the hole for at least one part lead is located at a grid intersection of the modular dimensioning system and the other holes of the pattern are dimensioned from the grid location or from datum origin.

- b. A hole pattern where the center of the pattern is located at a grid intersection of the modular dimensioning system and all holes of the pattern are dimensioned from that grid location or from datum origin.

. . .

5.3.6 <u>Indexing holes</u>. If indexing holes are to appear on the printed-wiring board, they shall be dimensioned on the master drawing.

.

5.4 Eyelets and standoff terminals. Eyelets and standoff terminals are to be considered components and specified on the assembly drawing.

5.4.1 <u>Material</u>. The eyelets shall be made of copper conforming to QQ-C-576. Standoff terminals shall be made of brass conforming to QQ-B-626 or bronze conforming to QQ-B-750.

5.4.2 Finish. The eyelets shall be tin-lead plated and fused (see 5.6.4.5). The standoff terminal shall be finished in accordance with 5.6.4.5 or 5.6.4.6 after having been underplated with 0.0001 inch (0.003 mm) minimum copper in accordance with MIL-C-14550.

5.4.3 Flange design. The flange used to make electrical contact to the terminal area shall be of the funnel flange type. The included angle of the flange shall be between 35 and 120 degrees. The rolled or flat flange shall be used when there will be contact with unclad material.

5.5 Plated-through holes. The maximum diameter of the plated-through hole shall not be more than 0.028 inch (0.71 mm) larger than the nominal of the inserted lead or the nominal diagonal of a flat ribbon lead, as shown on figure 15. The minimum diameter of the plated-through hole shall be not less than 0.006 inch (0.15 mm) larger than the nominal diameter of the inserted lead or nominal diagonal of a flat ribbon lead. Unless otherwise specified, the hole size shall be the finished plated size after solder coating or solder plating. Plated-through holes used for functional interfacial connections shall not be used for the mounting of devices which put the plated-through hole in compression. Plated-through holes used for functional interfacial connections shall not be used for the mounting of eyelets, standoff terminals, or rivets. The thickness of electrolytic copper plating in the hole shall be 0.001 inch (0.03 mm), minimum. The walls of plated-through holes shall be solder coated [see 5.6.4.6] or tin/lead plated and fused [see 5.6.4.5] as part of surface conductive cover requirements [see 5.6.4]. Solder coating or tin-lead plating does not apply to plated-through holes which are internal to the printed-wiring board and do not extend to the surface. The end product diameter of plated-through holes shall be specified on the master drawing.

5.6 <u>Materials</u>. Printed-wiring board designs shall be such that internal temperature rise due to current flow in the conductor (see 5.1.1) when added to all other sources of heat at the conductor/laminate interface, will not result in an operating temperature in excess of that specified for the laminate material (see table IV). Since heat dissipated by parts mounted on the boards will contribute local heating effects, the material selection shall take this local factor, plus the equipments general internal rise in temperature, plus the specified operating ambient temperature for the equipment into account. Hot spot temperatures shall not exceed the temperatures specified in table IV for the laminate material selected. Materials used (copper-clad, prepreg, copper foil, heat sink, etc.) shall be specified on the master drawing.

5.6.1 <u>Metal-Clad laminates</u>. The printed-wiring boards shall be fabricated from the metal-clad laminates specified in table 111 and copper foil types specified in IPC-CF-150. The type of board(s) that each material may be used in is indicated in table IV.

14

# MIL-ST0-275E

#### 31 December 1984

TABLE IV. Clad laminates.

| Specification | Base material                                                          | Operating<br>  temperature <u>1</u> /<br> | Board type  <br>    2   3  <br>                        |

|---------------|------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------|

| MIL-P-13949   | РХ<br>GE. GF <u>2</u> /<br>GB, GH, GP, GT, GX, GR, GY<br>GI <u>4</u> / | 105°C<br>125°C<br>150°C<br>170°C          | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

Ambient temperature plus the temperature rise caused by current in the con-1/ ductors (see 5.1.1). GE or GF laminates shall not be combined in one board with GI prepregs.

2/

37 See 6.4.

4/ When GI laminates are combined in one board with GE or GF prepregs, the temperature shall be 125°C.

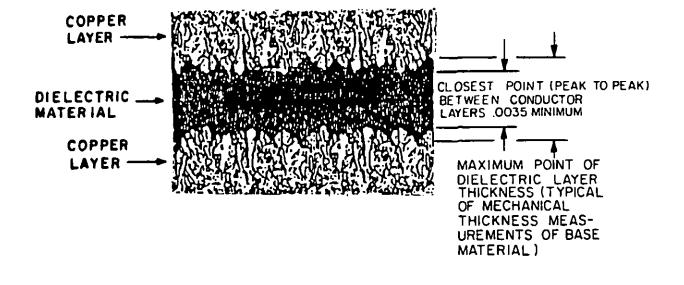

5.6.1.1 Minimum thickness of laminate. The thickness of the laminate per MIL-P-13949 used in type 3 printed-wiring boards shall be .002 inch (0.05 mm) or greater, provided the resulting dielectric layer in the finished board shall meet the requirements of 5.7.4. The thickness of the laminate per MIL-P-13949, used in type 1 and type 2 boards shall be as specified in the master drawing and shall meet the requirements of 6.4 (see figure 16).

#### 5.6.2 Bonding materials.

5.6.2.1 <u>Preimpregnated bonding layer (prepreg</u>). Prepreg used in type 3 printed-wiring boards shall conform to type GE, GF, or GI of MIL-P-13949. Type GE or GF prepreg shall not be used with type GI prepreg. If a specific type of bonding material is required, it shall be so specified on the master drawing.

5.6.2.2 Other bonding films. Other bonding films such as cast resin films and double sided resin coated polyimide films may be used to bond external heat sinks. internal thermal planes, or internal conductive planes provided the cured films meet the temperature requirements of the base material as specified in table 14, 5.7.4, and on the master drawing.

5.6.3 Copper circuitry layers. The thickness of finished copper conductors shall be not less than 1 ounce per square foot (0.0012 inches). Copper foil used shall be not less than 1/2 oz/ft<sup>2</sup> and must be plated up to the 1 oz/ft requirement. (Precautionary note: A reduction of copper thickness after processing can be expected.)

5.6.4 <u>Plating</u>. All external conductive patterns (plated-through holes, terminal areas, etc.) shall be solder coated or tin-lead plated, unless a permanent solder mask coating is used (see 5.6.5) or a heat sink is bonded to the external surface, or other plating is approved by the acquiring activity. When other platings are used on the same printed-wiring board in conjunction with solder coating or tin-lead plating, the area of overlap shall be kept to a minimum and no exposed copper shall be permitted at the interface between the other plating and the solder coating or tin-lead plating. No solder or tin plating shall be under other platings. Unless otherwise specified on the master drawing, surface and plated-through hole plating thicknesses shall meet the requirements specified in 5.6.4.1 through 5.6.4.6.

5.6.4.1 <u>Electroless copper plating</u>. An electroless deposition system shall be used as a preliminary process for providing the conductive layer over nonconductive materials for subsequent electrodeposition of metal in plated-through holes.

5.6.4.2 <u>Electrolytic copper plating</u>. All electrolytically deposited copper plating shall be performed in accordance with MIL-C-14550, and shall have a minimum purity of 99.5 percent as determined by ASTM-ES3. The minimum thickness shall be .001 inch (0.03 mm).

5.6.4.3 <u>Gold plating</u>. All electrolytically deposited gold shall be in accordance with MIL-G-45204, type II, class 1. The minimum thickness shall be 0.000050 inch (0.0013 mm); the maximum thickness shall be 0.0001 inch (0.003 mm) on areas that are to be soldered. A low stress nickel shall be used between gold overplating and copper (see 5.6.4.4).

5.6.4.4 <u>Nickel plating</u>. All electrolytically deposited nickel plating shall be low stress and conform to QQ-N-290, class 2, except the minimum thickness shall be .0002 inch (.005 mm).

5.6.4.5 <u>Tin-lead plating</u>. Tin-lead plating shall be in accordance with MIL-P-81728. The tin-lead shall be .0003 inch (.008 mm) thick minimum, as plated on the surface. Fusing shall be required on all tin-lead plated surfaces.

5.6.4.6 <u>Solder coating</u>. Unless otherwise specified, solder coating shall be in accordance with composition 5n60, Sn62, or Sn63 of QQ-S-571. The solder coating thickness shall be 0.0003 inch (0.008 mm) minimum, as coated (see 6.2.12 for surface mounted components).

5.6.5 <u>Solder mask</u>. Polymer mask coatings shall meet the requirements of IPC-SM-840, class 3 and, when required, shall be specified on the master drawing.

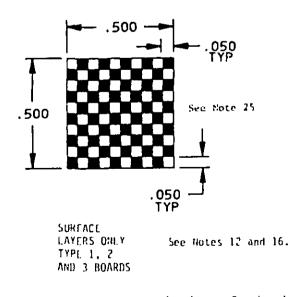

5.6.5.1 Solder mask over melting metals. Polymer mask coatings do not typically adhere to molten metals. When coatings are required over melting metal (such as solder) with areas of metal larger than 0.050 inch (1.3 mm) in two directions, the design shall provide relief through the metal to the printed-wiring substrate. The relief shall be at least 0.010 inch by 0.010 inch (0.25 mm by 0.25 mm) in size and located on a grid no greater than 0.250 inch (6.4 mm).

5.6.5.2 <u>Solder mask over nonmelting metals</u>. When polymer mask coatings are required over nonmelting metals (such as copper), the design shall provide that conductor areas not covered by the mask shall be tin/lead plated and fused (see 5.6.4.5) or solder coated (see 5.6.4.6). Bonding/adhesion promoters may be required (see 20.5).

5.7 Printed-wiring board dimensions. The board design shall meet the requirements specified in 5.7.1 through 5.7.5.

5.7.1 <u>Overall board dimensions</u>. Overall printed-wiring board dimensions (length and width), should coincide with lines of the modular dimensioning system.

5.7.2 <u>Board thickness</u>. The board thickness shall include metallic deposition, fusing, and solder mask, shall be measured across the board thickness extremities, and shall be as specified on the master drawing. In critical areas such as card guides, the thickness requirements shall be detailed on the master drawing.

5.7.3 Board thickness tolerance. The board thickness tolerance for types 1, 2, and 3 shall be as specified on the master drawing.

5.7.4 <u>Minimum thickness of dielectric layers</u>. Finished type 3 boards shall have a minimum of 0.0035 inch (.089 nm) of dielectric material between the consecutive conductor layers, when cured. Greater thicknesses should be considered for voltages greater than 100 volts. The dielectric material will be in accordance with MLL-P-13949 and may be comprised of laminate, prepreg and laminate, or multiple layers of prepreg. There shall be no less than two sheets of prepreg (B-stage) or laminate (C-stage), or combination thereof used between adjacent conductive layers. Other bonding films and thicknesses shall be specified on the master drawing (see 5.6.2.2 and figure 16).

NOTE: Thickness of dielectric layers shall be measured in accordance with MIL-P-55110.

#### 31 December 1984

5.7.5 Bow and twist. Unless otherwise specified on the master drawing, the maximum allowable bow and twist shall be 1.5 percent.

5.8 Detail board marking requirements. Individual printed-wiring boards and quality conformance test circuitry shall be identified in accordance with the master drawing and MIL-STD-130. Provision shall be made in the design for locating the traceability and date markings that are additionally required by the fabrication specification. The methods and materials for marking shall be specified on the master drawing. If ESD marking is required at the board level, it shall be specified on the master drawing. Marking shall be of a contrasting color to the background.

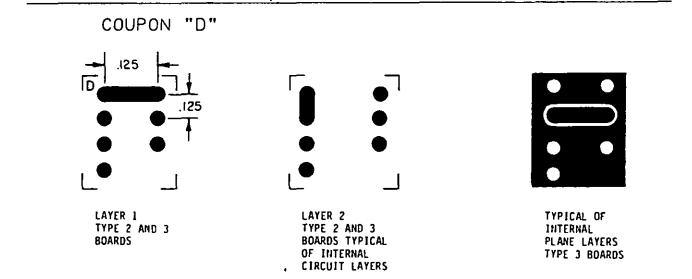

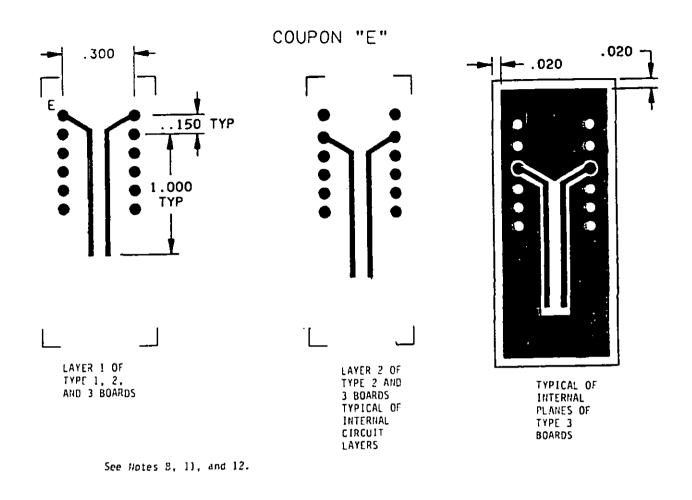

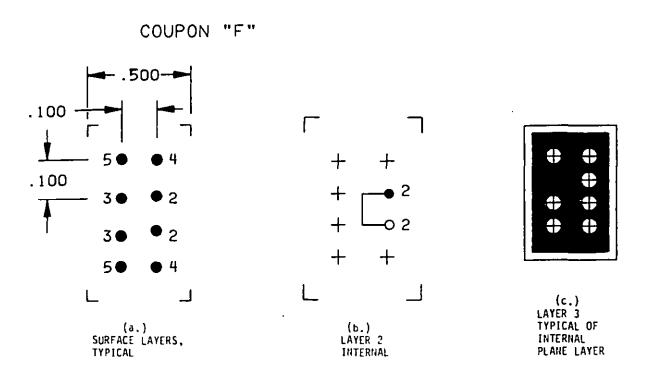

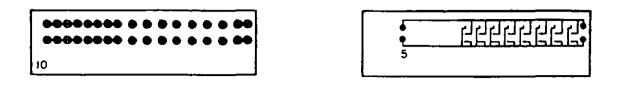

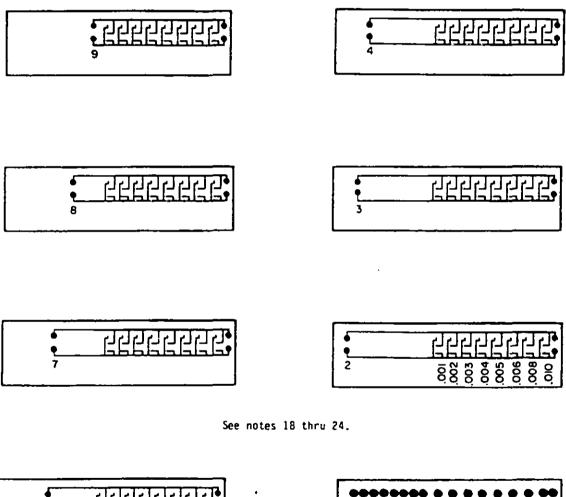

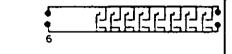

5.9 Quality conformance testing circuitry. The quality conformance test circuitry, comprised of the coupons shown on figure 1, shall be a part of every panel used to produce printed-wiring boards that are designed to this standard. The minimum number of coupons per panel and the requirements for positioning will be in accordance with table V. Coupons A, B, and F shall be positioned in accordance with 4.1 and figure 17. All other coupons may be positioned at optional locations. All coupons required shall be shown on the master drawing, artwork, and production master.

| Coupon                                  | Type 1                                                                             | Type 2                                                                             | Type 3                                                                                               |

|-----------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| l type<br>1                             | l board                                                                            | l board<br>I                                                                       | board l                                                                                              |

| <br>  Micro-<br>  section               |                                                                                    |                                                                                    | Twice per panel opposite T<br>corners location fixed by<br>lartwork (see figure 17)                  |

| B<br>Micro-<br>Section                  | Twice per panel opposite<br>lcorners location fixed by<br>lartwork (see figure 17) | Twice per panel opposite<br>Icorners location fixed by<br>lartwork (see figure 17) | corners location fixed by                                                                            |

| C<br>  Plating<br> <br>!                | loptional pattern defined                                                          | Ince per panel location<br>loptional pattern defined<br>lby artwork                |                                                                                                      |

| D<br>  Thermal<br>  shock               | Not required                                                                       | loptional pattern defined                                                          | Once per panel location  <br>loptional pattern defined  <br> by artwork                              |

| E <u>1/</u><br>Insulation<br>resistance | loptional pattern defined                                                          | loptional pattern defined                                                          | Once per panel location  <br>loptional pattern defined  <br> by artwork                              |

| F 2/<br>Registration                    | Not required                                                                       | Ì                                                                                  | Twice per panel opposite  <br> corners location<br> fixed by artwork<br> (see figure 1)              |

| J<br>  Solder<br>  mask                 | lpanel with solder mask<br>llocation optional                                      | lpanel with solder mask<br>llocation optional                                      | When required, once per 1<br>panel with solder mask<br>location optional<br>pattern fixed by artwork |

TABLE V. Conformance test circuitry.

1/ If the panel has solder mask, the E coupon shall be covered with the solder mask. Clearances of 0.010 +0.005 should be provided for all surface lands.

2/ Registration coupons are optional and may be used in lieu of microsection evaluation for registration.

#### 6. DETAIL PART MOUNTING REQUIREMENTS

6.1 Approved methods of attachment. Component leads shall pass through lead component holes and be attached or the component terminals or leads shall be surface mounted to the land pattern. Part attachment shall be described on the assembly drawing following the methods specified in 6.1.2 through 6.1.5.4. General mounting requirements shall be as specified in 6.1.1.

6.1.1 <u>Unclinched leads</u>. Unless otherwise specified, unclinched leads (either straight or partially bent for retention) shall be soldered in component holes or eyelets in accordance with IPC-S-815. If no clinching requirements are specified on the assembly drawing, unclinched lead termination shall apply.

6.1.1.1 <u>In unsupported holes</u>. Lead tip projection shall be required to extend from 0.020 inch (0.51 mm) minimum to 0.060 inch (1.5 mm) maximum from the surface of the foil.

6.1.1.2 In plated-through or eyeletted holes. The lead shall be required to extend at least to the surface of the plating or rim of the eyelet and extend no more than 0.060 inch (1.5 mm) from the plating surface or eyelet.

6.1.2 <u>Clinched leads</u>. When maximum mechanical retention of a lead or terminal is required by design, the lead or terminal shall be clinched. The component holes may be plated-through holes, unsupported holes, or eyeletted holes. Clinching requirements shall be defined on the assembly drawing. The lead end shall not extend beyond the edge of its land or its electrically connected conductor pattern in violation of the minimum spacing requirement. Partial clinching of leads for part retention shall be considered under the requirements of 6.1.1.

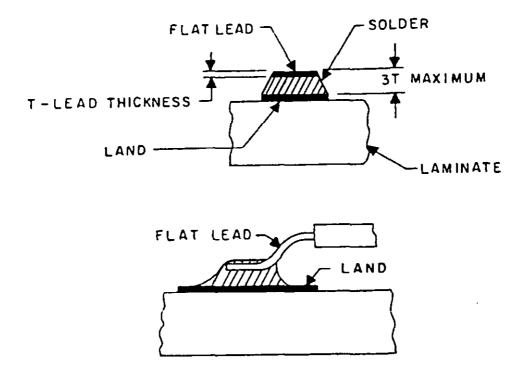

6.1.3 <u>Surface terminated ribbon leads</u>. Flat-wire ribbon leads may be attached to lands on the printed-wiring board. Connections shall be made by soldering only. The contact area between any lead and land shall be not less than a square having each side equal to the nominal width of the lead (see figure 9). Minimum conductor spacing indicated in 5.1.4 shall be maintained. Attachment details may be conveyed by an assembly drawing reference to 1PC-S-B15 (see figure 18). For additional mounting notes and considerations see 6.2.11.

6.1.4 <u>Surface terminated round leads</u>. With prior approval by the government acquiring activity, designs may stipulate that parts shall be attached with their round leads soldered to surface terminals (lands) without first passing through a hole. The lands shall be designed with proper shape and spacing to comply with proper soldering techniques (see IPC-S-815).

6.1.5 Standoff terminals, eyelets, or fasteners.

6.1.5.1 <u>Component attachment to standoffs</u>. Component attachment to standoff terminals shall be defined on the assembly drawing and meet the requirements of JPC-S-B15. Placement of terminals shall be specified to suit each application.

6.1.5.2 Attachment of standoffs to boards. A terminal of the funnel flanged type shall be specified wherever the flange must be soldered for electrical connection to a land. The included angle of such flange shall be between 35 and 120 degrees.

6.1.5.3 Eyelets. Eyelet applications used in design shall be in compliance with the following:

Attachment requirements - Interfacial connections shall not be made with eyelets. Eyelets installed at an electrically functional land shall be required to be of the funnel flange type.

6.1.5.4 <u>Fastening hardware</u>. The installed location and installation orientation shall be prescribed on the assembly drawing for any fastening devices such as rivets, machine screws, washers, inserts, nuts, and bracketing. Precautions such as the specification of tightening torque values shall be provided wherever general assembly practices might be inadequate or detrimental to the board assembly's structure or functioning.

6.2 Electrical part mounting. The following are requirements the designer shall consider and detail on the assembly drawing in specific notes or illustrations. All such electrical parts, hereafter referred to as components, shall also be selected so as to withstand the vibration, mechanical shock, humidity, and other environmental conditions the design must endure when the components are installed in accordance with 6.2.1 through 6.2.14.

6.2.1 One side only. Parts shall be mounted on only one side of the printed-wiring board assembly whenever possible.

6.2.2 <u>Accessibility</u>. Lands and terminals shall be located and spaced so that the terminations of each component are not obscured by any other component, or by any other permanently installed parts. Each component shall be capable of being removed from the assembly without having to remove any other component.

6.2.3 Design envelope. Unless otherwise detailed on the assembly drawing, the board edge is regarded as the extreme perimeter of the assembly, beyond which no portion of a component is allowed to extend. The designer shall prescribe the design envelope with due respect for maximum part body dimensions and the mounting provisions dictated by the board and assembly documentation.

6.2.4 Over conductive areas. No parts shall be mounted in direct contact with external conductor areas unless required for thermal dissipation. If design limitations require placement of parts over conductive areas, the part shall be mounted so that subsequent insulating coating will cover the conductive area under the part or conductive areas under parts shall be insulated or protected against moisture entrapment by applying conformal coating or a cured resin coating by laminating low-flow prepreg material in accordance with NIL-P-13949, or by solder masking over the area prior to mounting the part.

6.2.5 <u>Thermal transfer</u>. Components, which for thermal reasons require extensive surface contact with the board or with a heat sink mounted on the board, shall be protected from processing solutions at the conductive interface. To prevent risk of entrapment, compatible materials and methods shall be specified to seal the interface from entry of corrosive and conductive contaminants.

NOTE: Even totally nonmetallic interfaces that are prome to entrap fluids can have adverse effects on the fabricator's ability to pass required cleanliness tests.

6.2.6 <u>Components dissipating one or more watts</u>. Design for heat dissipation of components shall insure that the maximum allowable temperature of the board material is not exceeded under operating conditions specified in 5.6. Heat dissipation may be accomplished by requiring a gap between board and component, using a clamp or thermal mounting plate, or attaching a compatible, thermally conductive material working in conjunction with a thermal bus plane to the component.

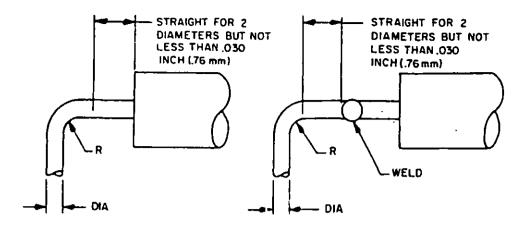

6.2.7 <u>Stress relief bends</u>. Lands and terminals shall be located by design so that components can be mounted or provided with stress relief bends in such a manner that the leads cannot overstress the part lead interface when subjected to the anticipated environments of temperature, vibration, and shock of MIL-P-28809. The lead length for stress relief and lead bend radius shall be in accordance with figure 19. Where lead bending can not be in accordance with figure 19 in order to achieve design goals, the bends shall be detailed on the assembly drawing.

6.2.8 <u>Mechanical support</u>. All parts weighing D.25 ounce (7.1g) or more per lead shall be supported by clamps or other specified means which will insure that the soldered joints and leads are not relied upon for mechanical strength.

6.2.9 <u>Axial-leaded parts</u>. Axial-leaded parts shall be mounted as specified on the approved assembly drawing and mounted so that a portion of the body is as close to the printed-wiring hoard as possible. The leads shall be shaped in accordance with 6.2.7. This does not apply to parts mounted on standoff terminals (see 6.1.5.1).

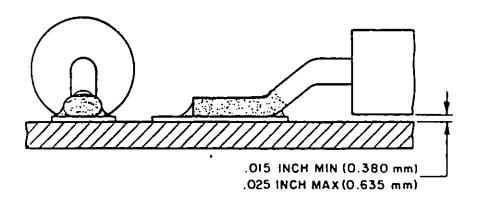

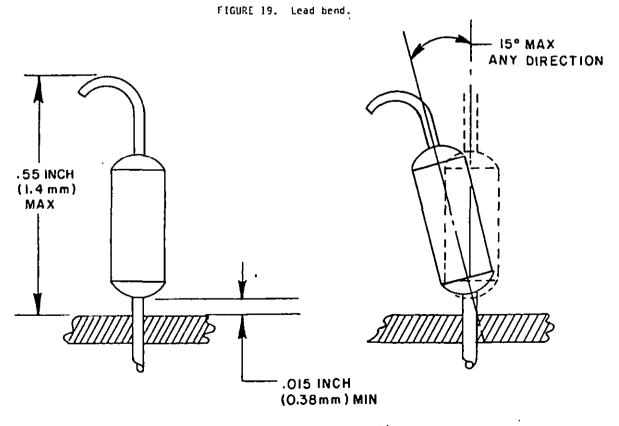

6.2.9.1 <u>Perpendicular mounting</u>. Axial-leaded components weighing less than 0.50 ounce (14g) may be mounted on the assembly using perpendicular mounting criteria. The assembly drawing shall prescribe a minimum of 0.015 inch (0.38 mm) space between the end of the component body (or the lead-weld) and the board. Unless otherwise noted on the assembly drawing, components required to be perpendicularly mounted shall be installed with their major axis within \*15 degrees of a right angle with board surface. The maximum vertical height from the board surface shall be 0.55 inch (14 mm) (see figure 20).

6.2.10 <u>Nonaxial-leaded parts</u>. Nonaxial-leaded parts shall be mounted with the surface from which the lead projects a minimum of 0.010 inch (0.25 mm) above the printed-wiring board surface. Dimensioning of the required spacing under these components is generally not required unless the component package design could result in an assembly error. For thermal considerations see 6.2.5 and 6.2.6.

6.2.11 <u>Multiple-leaded components</u>. Multiple-leaded components (components with three or more leads), except multiple leaded components mounted to thermal planes or heat sinks, shall be mounted in such a manner that components are spaced off the board to facilitate cleaning, provide electrical isolation, and to prevent moisture traps. The necessary gap may be prescribed as an exceptional fabrication requirement by identifying the subject component and prescribing the required underbody clearance dimension or the gap may be achieved by virtue of the component's own standoff features. Unless otherwise specified, a clearance of 0.010 inch (0.25 mm) minimum applies.

6.2.11.1 <u>Spacers</u>. Special spacers (such as feet, ribs, or projections) with minimal contact may be prescribed to go under the component, provided they will not impair soldering or the assembly's performance.

6.2.11.2 <u>Sealing</u>. The need for a gap between component body and board may be avoided by requiring the interface under the component to be sealed with adhesive or a combination of adhesive and insulation material, which is compatible with the board, parts, and conformal coating. This option exists only if all lead terminations are external to the seal. Repairability shall not be precluded by the method or material selection.

<del>،</del> -

Ł

6.2.12 <u>Surface mounted components</u>. The requirements and considerations of 6.2.4 apply to this class of components. Space for cleaning shall be provided to reduce entrapment.

6.2.12.1 Flat-pack types with ribbon leads. Lead forming is a major design consideration and shall be detailed on the assembly drawing to provide for lead stress relief, fit to the land pattern, underbody clearance for cleaning, and any designed-in provisions for thermal transfer (see figure 18 and 6.1.3).

6.2.12.2 <u>Chip carrier type</u>. Leadless components may be attached to the surface of a land. The component shall be attached to the land of the printed-wiring board in a way that provides sufficient space under the body of the component to facilitate cleaning. Land pattern design shall facilitate adequate solder fillets between the conductor pattern and the component.

6.2.12.3 End-cap discrete components. End-cap discrete resistor and capacitor components and similar leadless end-cap discrete components shall be mounted to printed wiring or printed circuitry. The devices shall not be stacked nor shall they bridge spacing between other parts or components, such as terminals or other properly-mounted components.

6.2.12.4 <u>Surface mounting of flattened round leaded components</u>. Components with axial leads of round cross-sections shall be utilized for surface mounting only if the leads are coined or flattened for positive receding. For flattened round leads with original diameter of 0.025 inch (0.635 mm) or greater, the flattened thickness shall be 70 percent of the original diameter, minimum. For leads with an original diameter less than the 0.025 inch (0.635 mm), the flattened thickness shall be 50 percent of the original diameter, minimum. The body of a planar mounted axial leaded component should be spaced away from the board to facilitate cleaning.

6.2.13 Two-part connectors (plug and receptacle). Two-part connectors containing male and female quick disconnect electrical contacts and integral aligning hardware to assure proper mating of the contacts shall be specified as the only means to integrate plug-in printed-wiring assemblies. Their attachment and mounting methods are subject to the design concerns of 6.1, 6.2.3, and 6.2.4. Board connectors may be uniquely keyed in such a manner only insertion of the proper assembly is possible.

6.2.13.1 Wires. Use of hard wiring directly to plug in connector mounted printed-wiring board assemblies shall not be permitted. Plug in assemblies shall have all external electrical connections accomplished through the use of two-part connectors.